# Intersil RS-232 Transmitter/Receivers Provide High Speed and 15KV ESD Protection

**Application Note**

November 21, 2005

AN9799.2

Author: Gene Faherty

### Introduction

The Intersil family of high-speed, 15kV ESD-protected devices (HIN202E - HIN241E) offers the user unparalleled performance in RS-232 communication. The devices feature high speed (230kbits/s) ISDN-compatible operation together with exceptional  $\pm 15 kV$  ESD protection and offer a wide variety of RS-232 transmitter/receiver combinations to suit various applications.

The HIN202E - HIN241E interface circuits meet all EIA RS-232E and V.28 specifications and are ideally suited to those applications where  $\pm 12V$  supplies are not available. The devices require a single 5V supply and incorporate on-chip charge pumps and converter circuitry which derive the  $\pm 10V$  levels. In addition, the HIN203E, HIN205E, HIN233E and HIN235E require no external capacitors and are particularly suited for those applications where board space is critical. The HIN205E, HIN206E, HIN211E, HIN213E, HIN235E, HIN236E and HIN241E feature a low power shutdown mode and TTL three-state outputs. The typical current draw in the low power shutdown mode is  $1\mu A$ . The HIN213E also provides two active receivers in shutdown mode allowing for easy "wakeup" capability.

The family of HIN202E - HIN241E devices are designed to be used in modems, printers, terminals, desktops, laptops, notebooks, bar code scanners, portable instrumentation and any system requiring RS-232 communication. Portable, battery-powered, or handheld devices are inherently susceptible to electrical stress such as ESD. Their I/O ports conduct ESD noise which may likely zap a system unusable. ESD-protected RS-232 serial ports in this equipment eliminate the need for additional external protection in most applications.

### **Evolution**

With the "never ending" trend of shrinking technologies, submicron CMOS processes, higher pin count devices, higher operating frequencies and lower supply voltages, the importance of robust ESD protection becomes even more critical. With the smaller geometry devices comes reduced gate oxide thickness, shallow junctions, and higher resistive connections. These factors make these new devices inherently more susceptible to ESD damage, compromising the products reliability and performance.

### EOS/ESD

ESD (Electrostatic Discharge) which is a subset of EOS (Electrical Overstress), has become increasingly important and of major concern to the electronics industry as a whole and of particular importance to organizations such as EOS/ESD Association which has attempted to standardize this phenomena. Many manufacturers, realizing the significance of EOS/ESD, specify ESD protection limits when purchasing components. Virtually all electronic components can be damaged due to EOS/ESD and the costs associated with this damage has been estimated to be in the billions of dollars, industry-wide. Compounding these costs are the additional costs associated with the customer perception of the product's diminished quality and reliability.

To define EOS, or Electrical Overstress, it is typically generated by power supplies or test equipment and generally lasts from milliseconds to seconds and often results in a catastrophic failure. From an IC level, indications of an EOS event are blown metal lines, molten damage, and often, thermal damage. ESD or Electrostatic Discharge on the other hand is a subset of EOS. ESD events are typically characterized by much less power dissipation (limited energy), events last for much shorter periods, in the range of nanoseconds to milliseconds, and may result in catastrophic failures but frequently result in performance degradation or latent failures. Also, the cumulative effect of repeated exposure can lead to complete failure. Typical indications of ESD damage are gate oxide breakdown, junction spiking, or input leakage failures. ESD events typically occur with device handling by automated handlers or assembly. The fundamental mechanism of ESD is called "tribocharging". Tribocharging occurs when different materials come in contact with one another and then separate, such as the sole of a person's shoe as they walk across a carpet, or when an IC rubs against a rail on an automatic handler. The magnitude of the charge generated is dependent upon many factors such as type of materials, speed at which they rub together, and the relative humidity of the environment.

The extent to which a device can tolerate ESD is measured in kV. The actual definitions of an ESD failures varies among different vendors, some requiring complete functional failure of the device. Intersil defines an ESD failure in the strictest sense. After ESD "zapping" of the device it is subject to full production testing and any part failing to meet any of the DC parametric, AC propagation, or functional testing to the data sheet specifications, is rejected. Maintaining this strict level of testing assures the user the most reliable devices possible.

# ESD Testing

There are several test methods currently in use for ESD testing. These methods are:

- Human Body Model (HBM)

- · Machine Model (MM)

- · Charge Device Model (CDM)

- International Electromechanical Commission (IEC61000-4-2 previously IEC801-X series)

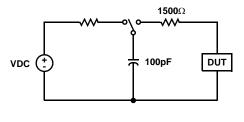

The Human Body Model (HBM) essentially charges a 100pF capacitor in increasing voltages in steps of 100V (100V, 200V, 300V, etc.) and then discharges the capacitor through a  $1500\Omega$  resistor into the device pin. (Figure 1). This model simulates that of a human finger contacting a device pin. Specifications that apply to HBM testing are MIL-STD-883, ESD Association Standard EOS/ESD-S5.1-1993 and JEDEC's Test method A114A.

FIGURE 1.

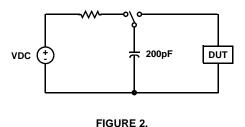

The next, Machine Model (MM), is similar to the HBM. The MM charges a 200pF capacitor in increasing voltages in steps of 100V and then discharges the capacitor directly into the device pin. This model simulates a worst case HBM or that of a charged metallic object contacting a device pin. (Figure 2) Specifications that apply to the MM are ESD Association Standard EOS/ESD-DS5.2-1992 and JEDEC's Test method A115A and EIAJ's IC-121-1988 test Method 20.

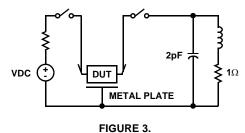

The Charged Device Model (CDM) directly charges the device pin to increasing voltage levels through a  $300M\Omega$  or  $1G\Omega$  resistor then discharges the pin, to ground, through  $1\Omega$  resistor. (Figure 3) This model simulates a device pin acquiring a static charge and then touching ground. This scenario has been observed on lead trimming assemblies where the IC devices run along a rail, developing a static charge, and then contacts a

metal stop at the bottom. Standards that apply to the CDM are the ESD Association Standard EOS/ESD-DS5.3-1993 and JEDEC's Test method C101.

Next is the International Electromechanical Commission Human Body Model (IEC61000-4-2). The IEC61000 is actually a system level specification but some customers have been applying this standard to individual IC's. The IEC61000-4-2 again simulates that of a human finger. Two modes are specified within the test. The Contact Mode and the Air Discharge Mode. As its name implies, the contact mode simulates actual contact made to device pin, whereas in the air discharge mode, after charging, the device pin is approached with a probe until arc occurs. With the air discharge mode, the results are influenced by humidity, temperature, barometric pressure and closure rate of probe.

The IEC standard is being applied to all systems and equipment entering the market of the European Union (EU). OEMs are playing it safe by using ESD-protected components inside their systems although the standard is not directed to individual integrated circuits (IC's). Whole systems are awarded the "CE" mark once they conform to the EU directive on electromagnetic compatibility.

### Benefits of HIN202E - HIN241E

The HIN202E - HIN241E series of devices offer the following levels of ESD protection:

| • | Human Body Model               | T <sub>OUT</sub> , R <sub>IN</sub> | ±15kV       |

|---|--------------------------------|------------------------------------|-------------|

| • | IEC61000-4-2 Contact Discharge | T <sub>OUT</sub> , R <sub>IN</sub> | $\pm 8kV$   |

| • | IEC61000-4-2 Air Gap           | T <sub>OUT</sub> , R <sub>IN</sub> | $\pm 15 kV$ |

| • | Human Body Model               | TIN, ROLIT                         | ±2kV        |

Simply touching or plugging in a cable can result in an ESD strike. Since the device I/O pins are most susceptible to an ESD strike (the pins that route off the board)  $T_{OUT}$  and  $R_{IN}$  are all protected to  $\pm 15 \text{kV}$  HBM.

In addition to the robust ESD and inherent latch-up protection provided by the HIN202E - HIN241E devices, is the high data rate capability. The guaranteed data rate of 230kbits/s far exceeds the RS-232 requirement of 19.2kbits/s. These features together with the variety of transmitter/receiver combinations, low power shutdown, three-state mode, active receivers in shutdown, single 5V supply,  $0.1\mu F$  or no capacitor versions and a variety of package options provide the user a total solution for their RS-232 needs.

## **Application Note 9799**

#### SUMMARY OF ESD PROTECTION LEVELS OF VARIOUS RS-232 INTERFACE FAMILIES

|                                          | НВМ   | IEC61000-4-2<br>CONTACT DISCHARGE | IEC61000-4-2<br>AIR GAP |

|------------------------------------------|-------|-----------------------------------|-------------------------|

| Intersil HIN202E-HIN241E                 | ±15kv | ±8kV                              | ±15kV                   |

| Sipex SP200-SP213                        | ±10kV | -                                 | -                       |

| Maxim MAX202E-MAX213E                    | ±15kv | ±8kV                              | ±15kV                   |

| Linear Technology LT1130A/LT1140A Series | ±10kV | -                                 | -                       |

| Maxim MAX202E-MAX213E                    | ±15kv | ±8kV                              | ±15kV                   |

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com